[ad_1]

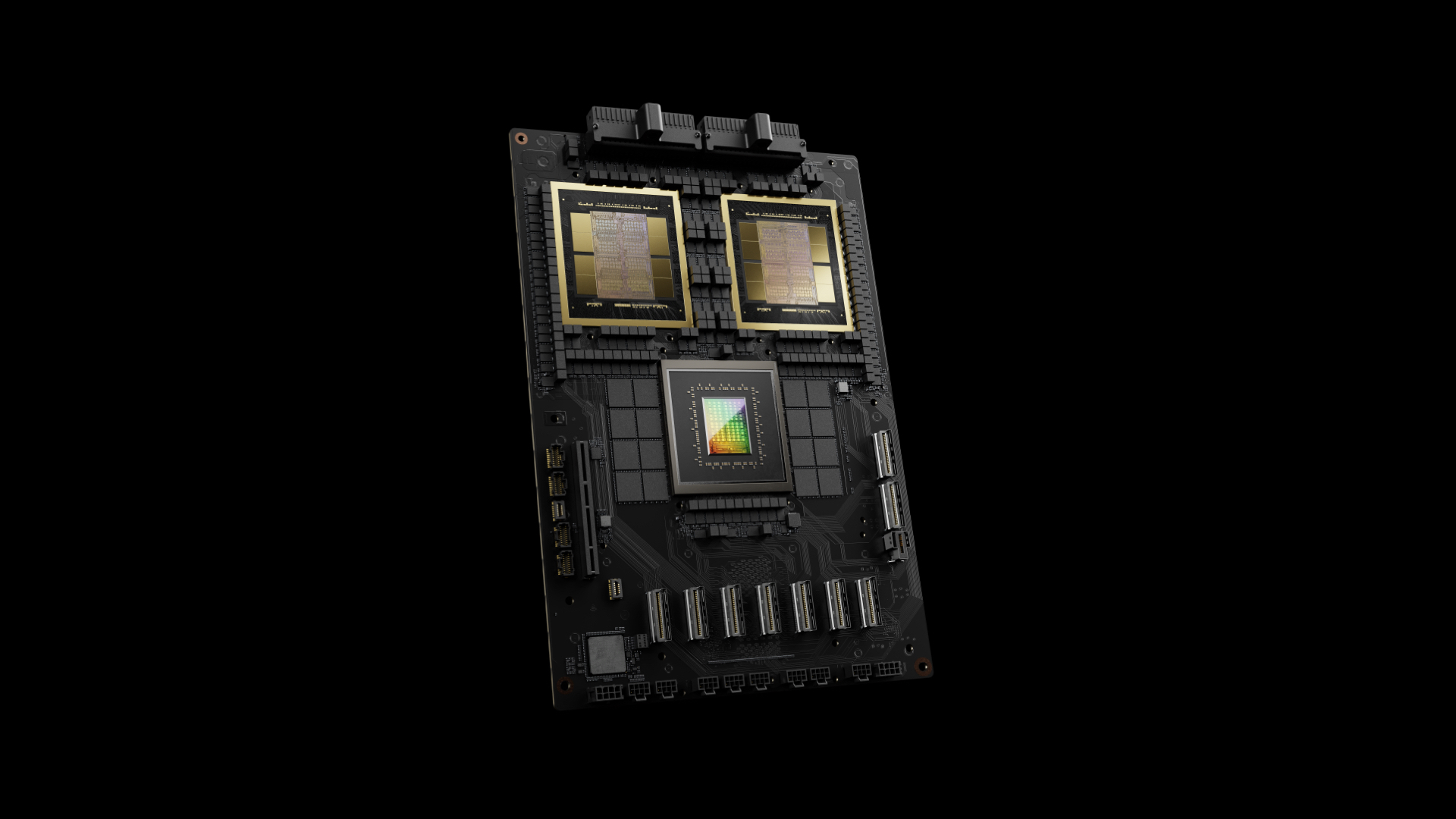

Demand for Nvidia’s bleeding-edge Blackwell dual-die designs is reportedly overtaking Nvidia’s lower-end single-die designs. TF Worldwide Securities analyst Ming-Chi Kuo from Medium experiences that the trillion-dollar GPU manufacturing big has up to date its Blackwell architecture roadmap to prioritize dual-die designs that includes CoWoS-L packaging.

Beginning within the first quarter of this yr, Nvidia will reportedly give attention to its 200 sequence Blackwell GPUs. Nonetheless, it is essential to notice that this solely contains multi-die variations of the 200 sequence, such because the GB200 NVL72 — single-die variations of the 200 sequence, such because the B200A, have been discontinued.

Likewise, Nvidia apparently plans to prioritize B300 sequence fashions that reap the benefits of a number of dies, particularly the GB300 NVL72. B300 GPU variants that solely use a single die can have a low-priority function in manufacturing as a result of larger demand for the multi-die variants. Nvidia’s high-priority Blackwell GPU fashions use TSMC’s extra superior CoWoS-L expertise. The discontinued B200A and the single-die B300 GPUs each use CoWoS-S.

On account of these modifications, sure suppliers will likely be hit “significantly arduous” as Nvidia prioritizes dual-die designs. Thus, the CoWoS-L packaging will likely be required to construct these fashions. These supplying Nvidia with CoWoS-S will endure the most important impression from Nvidia’s new roadmap.

Nonetheless, TSMC purportedly won’t be considerably impacted by these modifications. The Taiwanese semiconductor producer plans to prioritize CoWoS-L as its mainstream resolution, which aligns with Nvidia’s plans to make use of CoWoS-L as its dominant resolution. Moreover, transitioning from B200 to B300 manufacturing includes the identical FEoL course of, which is able to enhance manufacturing effectivity and cut back potential downtime. TSMC expects AI/HPC to be its key supply of development for 2025.

CoWoS-S and CoWoS-L, are packaging technologies made by TSMC. CoWoS-S, or Chip on Wafer on Substrate with silicon interposer, gives excessive density interconnects and deep trench capacitors over a big silicon interposer space to accommodate parts equivalent to logic chipsets and HBM reminiscence.

CoWoS-L combines CoWoS-S with InFO, or Combine Fan-Out applied sciences, to supply better flexibility when utilizing an interposer with an LSI or Native Silicon Interconnect chip for die-to-die interconnect. These bridges are a important a part of the design, and are why multi-chip Blackwell GPUs have been in a position to keep their 10TB/s NVLink interconnect.

[ad_2]